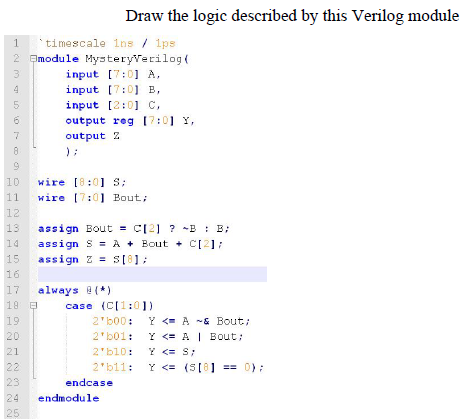

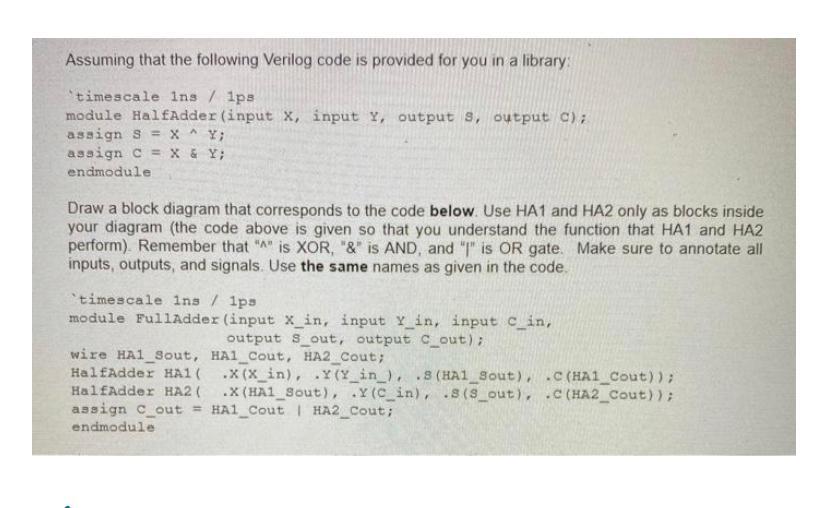

Lecture 5. Verilog HDL #1 Prof. Taeweon Suh Computer Science & Engineering Korea University COSE221, COMP211 Logic Design. - ppt download

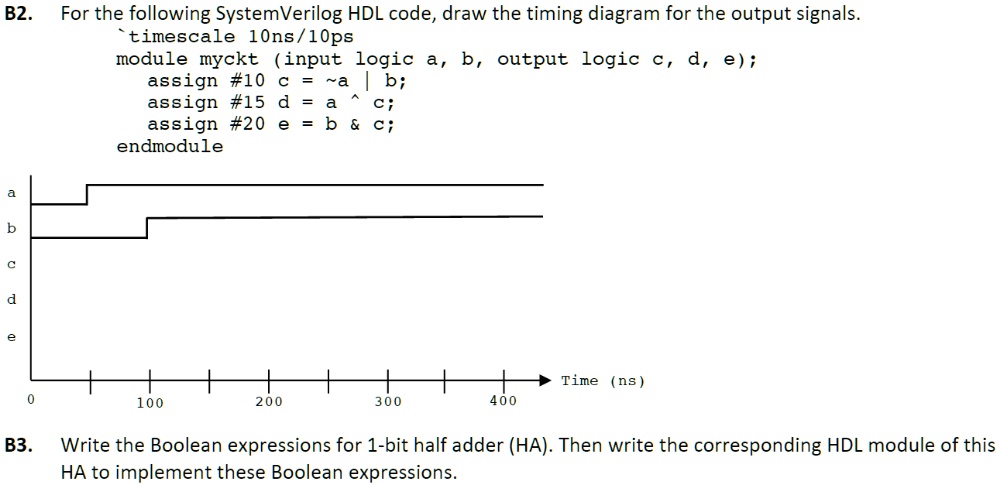

SOLVED: WRITE IN VERILOG HDL CODE B2. For the following SystemVerilog HDL code, draw the timing diagram for the output signals. Timescale 10ns/10ps module myckt (input logic a, b, output logic c,

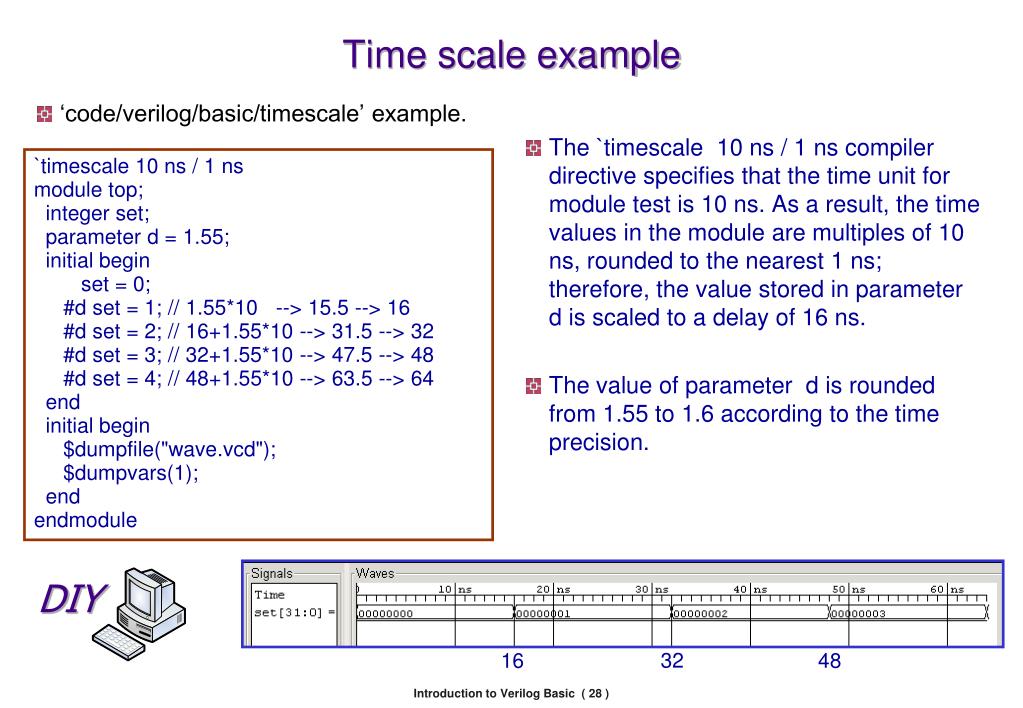

PPT - Verilog Basic Language Constructs - Lexical convention, data types and so on - PowerPoint Presentation - ID:2223612

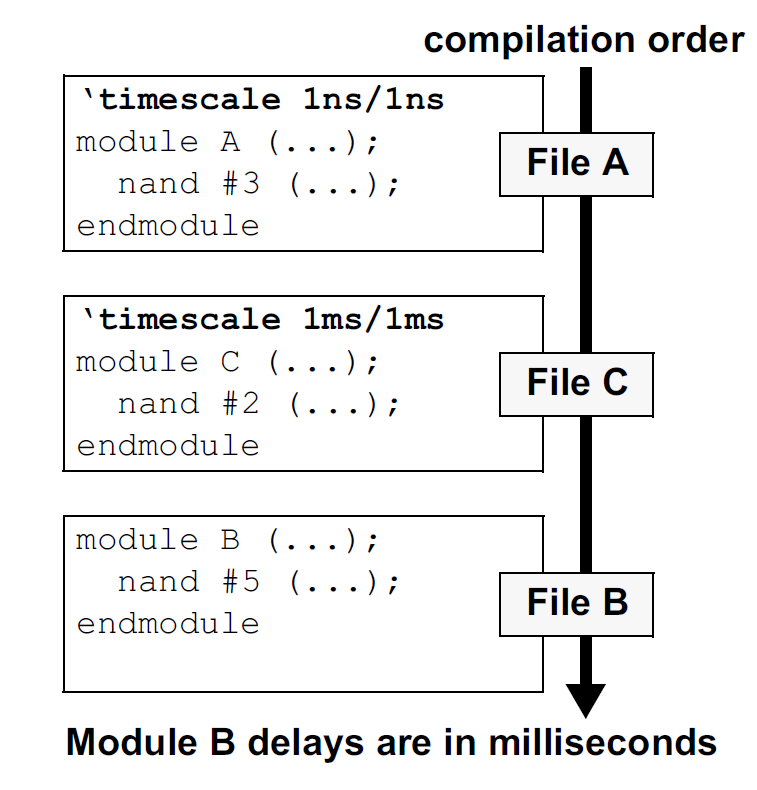

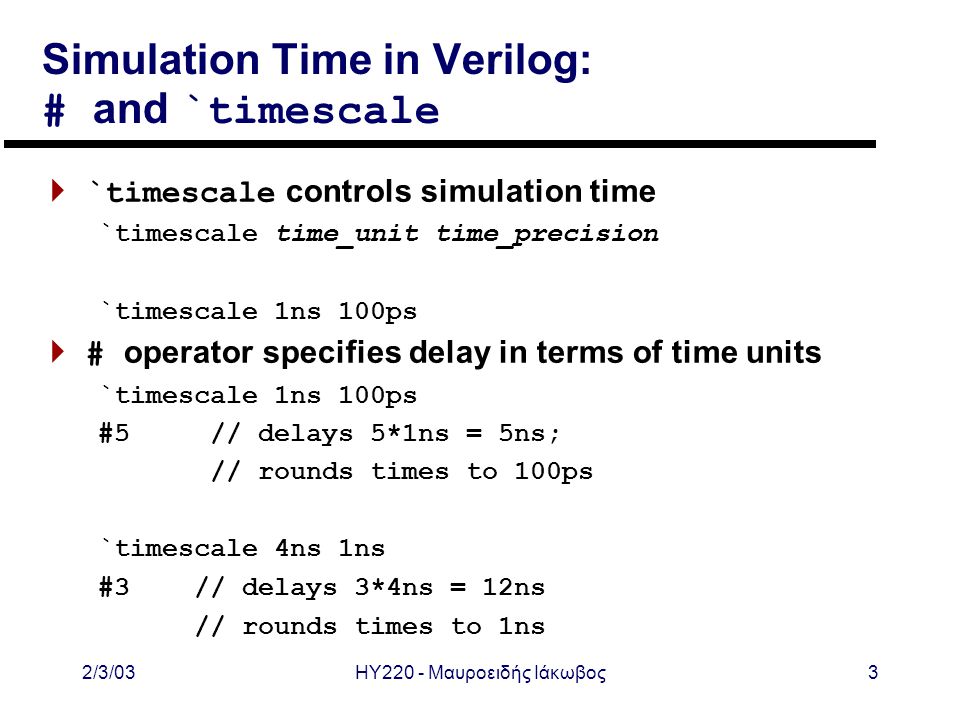

2/3/03ΗΥ220 - Μαυροειδής Ιάκωβος1 Delays in Behavioral Verilog - Interassignment Delay Key idea: unlike blocking delay, RHS is evaluated before delay. - ppt download

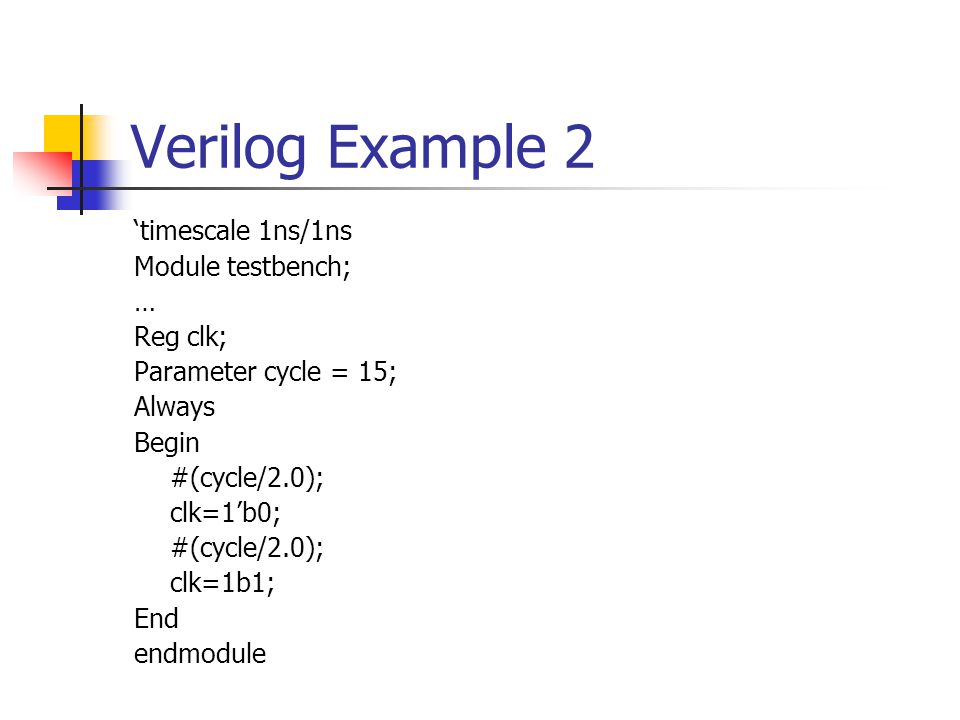

Stimulus and Response. Simple Stimulus Verifying the Output Self-Checking Testbenches Complex Stimulus Complex Response Predicting the Output. - ppt download